- 您现在的位置:买卖IC网 > Sheet目录251 > SGN08G72G1BB2SA-CCWRT (Swissbit NA Inc)SDRAM DDR3 8GB 204 SO-UDIMM

Preliminary Data Sheet

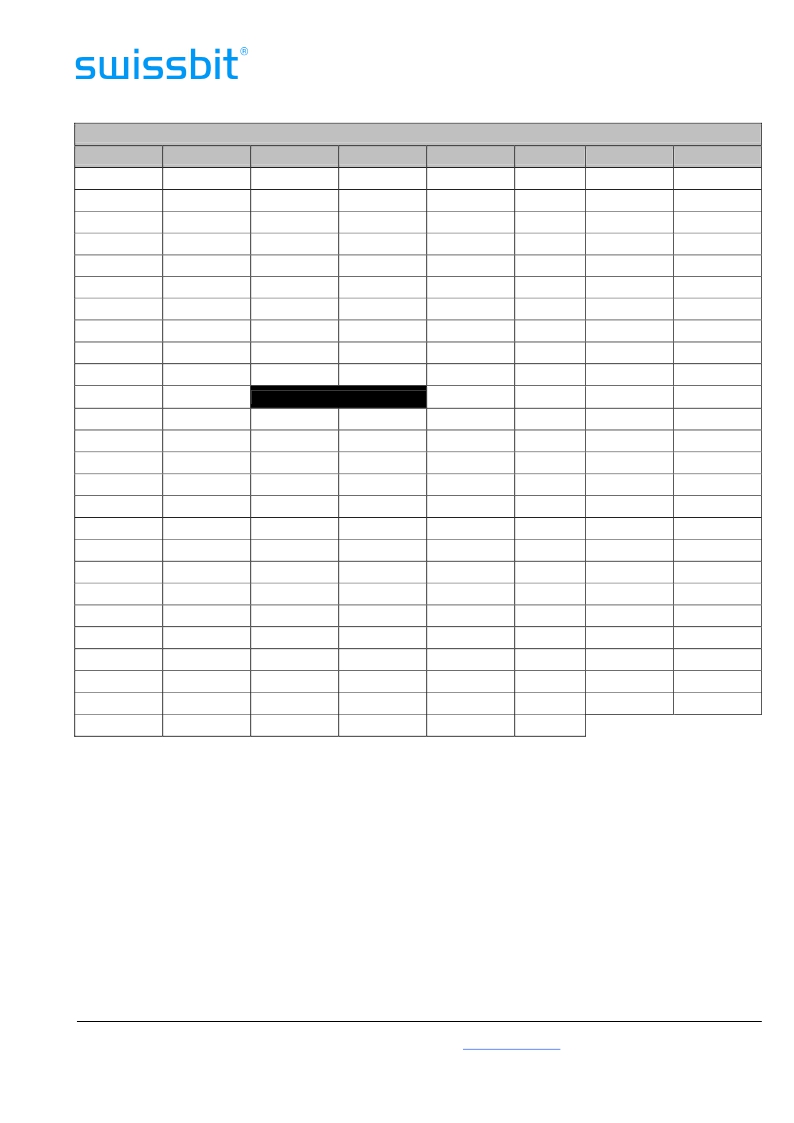

Backside

Rev.0.9

20.09.2011

Pin

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

Symbol

V SS

DQ4

DQ5

V SS

DQS0#

DQS0

V SS

DQ6

DQ7

V SS

DQ12

DQ13

V SS

DM1

Reset#

V SS

DQ14

DQ15

V SS

DQ20

DQ21

DM2

V SS

DQ22

DQ23

V SS

Pin

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

Key

Symbol

DQ28

DQ29

V SS

DQS3#

DQS3

V SS

DQ30

DQ31

V SS

CB4

CB5

DM8

V SS

CB6

CB7

V REFCA

V DD

A15

A14

A9

V DD

A11

A7

A6

V DD

Pin

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

Symbol

A4

A2

BA1

V DD

CK1

CK1#

V DD

NC(S3#)

NC(S2#)

RAS#

V DD

ODT0

ODT1

A13

V DD

DQ36

DQ37

V SS

DM4

DQ38

DQ39

V SS

DQ44

DQ45

V SS

DQS5#

Pin

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

Symbol

DQS5

V SS

DQ46

DQ47

V SS

DQ52

DQ53

V SS

DM6

DQ54

DQ55

V SS

DQ60

DQ61

V SS

DQS7#

DQS7

V SS

DQ62

DQ63

V SS

EVENT#

SDA

SCL

V TT

(Sig): Signal in brackets may be routed to the socket connector, but is not used on the module

Swissbit AG

Industriestrasse 4

CH – 9552 Bronschhofen

Fon: +41 (0) 71 913 03 03

Fax: +41 (0) 71 913 03 15

www.swissbit.com

eMail: info@swissbit.com

Page 4

of 15

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SGP1200-12G

FRONT END AC/DC 1133W 12V

SL05.TCT

TVS ARRAY DATA INTFC SOT-23

SL24T1G

TVS LO CAP 300W 24V ESD SOT23

SLD10U-022-B

DIODE TVS AXIAL HI-POWER

SLP-2-413-01

SNAP LOCK PINS TEAR-DROP .413"

SLVU2.8-4.TBT

IC TVS ARRAY 4-LINE 2.8V 8SOIC

SLVU2.8-8.TBT

IC TVS ARRAY 8-LINE 2.8V 8SOIC

SLVU2.8HTG

TVS DIODE ARRAY 1CH SOT23

相关代理商/技术参数

SGN08G72G1BB2SA-DCRT

制造商:SWISSBIT 功能描述:DDR3 SO-DIMM 8 GB 1600/CL11 - Trays 制造商:SWISSBIT NA INC 功能描述:DDR3 8GB SODIMM

SGN08G72G1BB2SA-DCWRT

功能描述:MODULE DDR3 SDRAM 8GB 204SOUDIMM 制造商:swissbit na inc. 系列:- 零件状态:过期 存储器类型:DDR3 SDRAM 存储容量:8GB 速度:1600MT/s 封装/外壳:204-SO-UDIMM 标准包装:100

SGN2M056TG

制造商:Panasonic Industrial Company 功能描述:DOOR

SGN72288FH8P6PH

制造商:SMART Modular Technology Inc 功能描述:MEMORY MODULE - Trays

SGN72568FH8P0PH

制造商:SMART Modular Technology Inc 功能描述:ECC 256MX8 .94" DDR3-1333 NVDIMM - Trays

SGN72568FH8YZPH

制造商:SMART Modular Technology Inc 功能描述:2GB 1.18" MINI-NVDIMM, 256MX8 - Trays

SGN-75

制造商:EGS ELECTRICAL GROUP 功能描述:GSK 4.625X1.562X0.125 NEO

SGNE010MK

制造商:SUMITOMO ELECTRIC Device Innovations Inc 功能描述:GaN HEMTs, MK16dB, 3.5GHz, 100mA, Bulk